|

RADIO INSTITUTO CURSO DE

CIRCUITOS DIGITALES LECCIÓN Nº 7 LOS

INTEGRADOS SECUENCIALES COMERCIALES EL BIESTABLE

CD4013 - LOS DISPARADORES SCHMITT CD4093 Y CD40106 - LOS UMBRALES DE

HISTÉRESIS VT+ VT- Y VH - CONTADOR DIVISOR X 2 - LLAVE OSCILANTE - 4013 COMO MONOESTABLE

- DISTINTAS CONFIGURACIONES - CONFORMACIÓN DE ONDAS SENOIDALES EN ONDAS

CUADRADAS - ELIMINACIÓN DE RUIDO ELÉCTRICO - ASTABLE CON 4093 - ASTABLE CON

40106 - VERIFICACIÓN EN LA PLAQUETA DE ENSAYOS En

la presente lección abordaremos el estudio de tres integrados de la familia

CMOS muy conocidos y de uso corriente en circuitos digitales. Nos referimos

al biestable CD4013 y a los disparadores

SCHMITT CD4093 y CD40106. Veremos las formas clásicas de conexión y otras

variantes que se pueden lograr con ellos y que no es común encontrar en los

textos. EL

BIESTABLE CD 4013 Este

circuito integrado es un doble flip-flop tipo D fabricado por varias compañías, entre

ellas la firma NATIONAL de cuyo manual hemos extractado los datos para el

estudio del mismo. Es

probablemente el flip-flop integrado

mas usado en distintos circuitos digitales dado las características y

flexibilidad operativa que ofrece. En

la presente lección estudiaremos su tabla de verdad y la forma de realizar

las conexiones de sus entradas a fin de lograr la operación que se necesite.

En la figura 1 podemos observar el resumen de datos que brinda la firma

NATIONAL, la disposición de terminales de los dos flip-flop encapsulados y la tabla de verdad

correspondiente. Hemos

numerado la tabla del 1 al 6 para mayor claridad en el análisis de la misma. 1

- En este renglón se observa que las entradas están todas en 0, por lo tanto

la transición en sentido positivo del pulso de reloj, no tiene efecto en las

salidas, por lo que la salida Q se mantiene en 0 y 2

- Aquí podemos ver la forma clásica de conectar este flip-flop, ya que para lograr la conmutación del mismo, las

entradas set y reset deben estar a potencial 0 y el

dato a 1. En esta condición, cuando en la entrada reloj se presente un pulso

de transición positiva el flip-flop cambia de estado y se mantiene en él, aún

después de desaparecer dicho pulso. 3

- El pulso de reloj es de transición negativa, es decir de 1 hacia 0, por lo

tanto aunque las entradas set y reset están bien

polarizadas, no conmutará independientemente del nivel de la entrada dato,

que puede ser 1 ó 0, ya que como hemos dicho, solo lo hace en la transición

positiva. 4

- En este caso las X que se observan en las entradas de reloj y dato

significan que es irrelevante el nivel que tengan ya que al estar a 1 la

entrada reset, el flip-flop no

producirá ningún cambio. 5

- Aquí podemos ver que el comportamiento es igual a los flip-flop que ya hemos

estudiado y realizado en la práctica con compuertas, es decir los clásicos

R-S (reset-set). Tampoco ahora tiene importancia la

polaridad de las entradas de reloj y dato, las que pueden estar a 1 ó 0, ya

que el cambio de estado se produce llevando el nivel de set

a 1, y se mantendrá en él aunque esta entrada vuelva a 0. Solo volverá al

estado anterior (reposo) llevando momentáneamente la entrada reset a 1.

6

- Esta es una situación en la cual continúa funcionando como R-S, pero con la

particularidad de ser seguidor de la señal presente en la entrada set. Sigue sin tener importancia los niveles de reloj y

dato. Al llevar el set a 1, la salida Q cambia

también a 1, pero no cambia la salida Esto

es así porque la entrada reset está a nivel 1, y como ya sabemos con positivo

en este terminal el flip-flop se mantiene en estado de reposo. A

continuación vamos a comprobar toda la tabla de verdad empleando para ello la

plaqueta de ensayos. Inserte en la misma el integrado CD4013 y conecte el

mismo de acuerdo al diagrama de la figura 2. Como verá usamos uno solo de los

dos que encierra el encapsulado.

FIG.

2 - COMPROBACIÓN DE LA TABLA DE VERDAD DE UN CD4013 Observe

que en todas las entradas se han dispuesto resistencias de 10K, con lo que

podría pensarse que de este modo no se logran los niveles absolutos, sin

embargo recuerde lo ya estudiado en lecciones anteriores; Las entradas en los

circuitos CMOS son de muy alta impedancia y no consumen corriente, por lo

tanto cualquier estado sea 1 ó 0 puede lograrse a través de resistencias,

incluso de alto valor. Por supuesto que si no son necesarias no se colocarán

y serán reemplazadas por conexiones directas. Para realizar esta

comprobación, sí son necesarias, a fin de lograr los dos niveles fácilmente. También

se insertarán cuatro alambres de conexiones para efectuar los cambios de

polaridad de dichas entradas. El

diodo led se ha dispuesto a través de una

resistencia de 2,2 K a fin de no sobrecargar la salida Q y evitar poner un

transistor para abastecerlo. Las

entradas set y reset están normalmente a 0 y se

llevan a 1 mediante los alambres de conexiones que hemos insertado en la

línea de +B. Las entradas dato y reloj

(CL) están normalmente a 1 y se llevan a 0 mediante los 2 alambres conectados

a masa. En

la entrada reloj, los pulsos se producen al tocar o retirar el alambre del terminal 3. Al llevarlo a masa se produce un pulso de

flanco descendente o transición negativa, al retirarlo se produce a la

inversa, flanco ascendente o transición positiva. Bien,

solo resta establecer los estados y comprobar lo dicho en la tabla de verdad.

En cada operación recuerde que el último paso ha de ser el pulso de reloj, es

decir que previamente se habrán polarizado las otras entradas de acuerdo al

renglón elegido de la tabla. El

diodo led solo brillará ante la

conmutación o puesta a 1 del flip-flop. En ocasiones, al darle alimentación al circuito

el flip-flop sale

cambiado, por lo que el led estará

encendido, la "puesta a 0" o reposo ya sabe que se logra al aplicar

un 1 en reset.

FIG.

2 - COMPROBACIÓN DE LA TABLA DE VERDAD DE UN CD4013 Observe

que en todas las entradas se han dispuesto resistencias de 10K, con lo que

podría pensarse que de este modo no se logran los niveles absolutos, sin

embargo recuerde lo ya estudiado en lecciones anteriores; Las entradas en los

circuitos CMOS son de muy alta impedancia y no consumen corriente, por lo

tanto cualquier estado sea 1 ó 0 puede lograrse a través de resistencias,

incluso de alto valor. Por supuesto que si no son necesarias no se colocarán

y serán reemplazadas por conexiones directas. Para realizar esta

comprobación, sí son necesarias, a fin de lograr los dos niveles fácilmente. También

se insertarán cuatro alambres de conexiones para efectuar los cambios de

polaridad de dichas entradas. El

diodo led se ha dispuesto a través de una

resistencia de 2,2 K a fin de no sobrecargar la salida Q y evitar poner un

transistor para abastecerlo. Las

entradas set y reset están normalmente a 0 y se

llevan a 1 mediante los alambres de conexiones que hemos insertado en la

línea de +B. Las entradas dato y reloj

(CL) están normalmente a 1 y se llevan a 0 mediante los 2 alambres conectados

a masa. En

la entrada reloj, los pulsos se producen al tocar o retirar el alambre del terminal 3. Al llevarlo a masa se produce un pulso de

flanco descendente o transición negativa, al retirarlo se produce a la

inversa, flanco ascendente o transición positiva. Bien,

solo resta establecer los estados y comprobar lo dicho en la tabla de verdad.

En cada operación recuerde que el último paso ha de ser el pulso de reloj, es

decir que previamente se habrán polarizado las otras entradas de acuerdo al

renglón elegido de la tabla. El

diodo led solo brillará ante la

conmutación o puesta a 1 del flip-flop. En ocasiones, al darle alimentación al circuito

el flip-flop sale

cambiado, por lo que el led estará

encendido, la "puesta a 0" o reposo ya sabe que se logra al aplicar

un 1 en reset.

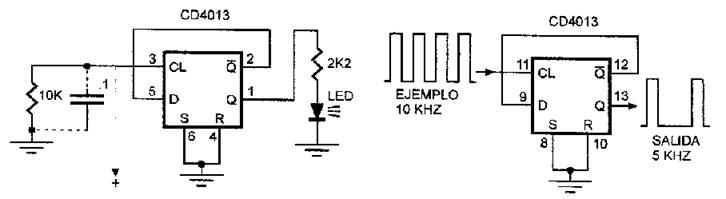

FIG.

3 - LLAVE OSCILANTE (VAIVÉN) DIVISOR X 2 En la figura 3 representamos la forma de

conectar este biestable para lograr un

divisor por 2, y el mismo circuito como llave oscilante o vaivén. En

el caso del divisor, a modo de ejemplo establecimos una frecuencia de

10 Khz, con lo que se obtiene en la salida Q 5

Khz. La llave oscilante o vaivén, cambia de estado con cada pulso de flanco

ascendente en la entrada reloj. Se ha dispuesto el diodo led y el alambre de conexiones para que el alumno

realice este trabajo práctico. Al

realizar los toques con el alambre, se puede producir ruido eléctrico por lo

que el circuito producirá mas de un cambio

que se observará en el led, pudiendo quedar

éste apagado o encendido (efecto de rebote), pruebe conectar un capacitor de .1 de la entrada de reloj a masa y

seguramente desaparecerá este efecto. En

la figura 4 vemos otras formas posibles de conexión para lograr una llave. En

estos casos son necesarias dos señales de control; una para ponerlo en

servicio o puesta a 1 y otra para llevarlo al reposo o puesta a 0.

FIG.

4 OTRAS VARIANTES DE CONEXIÓN En

"A" se trabaja para la puesta a 1 con la entrada de reloj, y para

la puesta a 0 con el reset. Para

lograr la puesta a 1 es necesario que la entrada dato se encuentre en 1. Ver

tabla de verdad renglón 2. Para

lograr el estado inicial (reposo o puesta a 0), se aplica un pulso de iguales

características que el de la entrada reloj, es decir, de flanco ascendente,

en la entrada reset. Ver renglón 4 de la tabla. En

"B" lo utilizamos como los clásicos flip-flop R-S, es decir la entrada set

para la puesta a 1 y la entrada reset para la puesta a 0, en ambos casos se

aplican pulsos de flanco ascendente. Las

entradas de reloj y dato, en este caso son irrelevantes, es como si no

existieran, por lo tanto no tiene importancia el nivel en ellas. Las hemos

conectado a masa porque no se deben dejar "al aire" ya que

adoptarían un estado intermedio o de indecisión, pero lo mismo funcionará si

las conectamos a +B. Ver tabla renglones 4 y 5. Los

pulsos de flanco ascendente los realizaremos mediante un alambre de

conexiones conectado en la línea de +B efectuando los toques sobre el terminal de las resistencias que está conectado con las

entradas correspondientes. FLIP-FLOP

CONECTADO COMO MONOESTABLE La

realización de un monoestable a partir del 4013 es muy simple y requiere tan

solo de una resistencia, un diodo y un capacitor,

como vemos en la figura 5. También en este caso se puede operar desde las

entradas reloj o set, obteniéndose los mismos

resultados.

FIG. 5 - DOS VARIANTES DE CONEXIÓN COMO

MONOESTABLE En

"A" de la figura 5 vemos como se conecta para ser operado desde la

entrada reloj, y en "B" desde la entrada set.

En ambos casos un pulso de transición positiva produce el cambio o puesta a

1, con lo cual la salida Q pasa al estado alto. A partir de este instante,

el capacitor conectado en el reset

comienza a cargarse. Cuando la magnitud de la tensión de carga supera el

estado intermedio, actúa la entrada reset produciendo un nuevo cambio que lo

pone en estado de reposo nuevamente. Este

ciclo se cumplirá siempre igual cada vez que reciba la "orden de

actuar'. Si dicha orden se efectúa desde la entrada set,

el comportamiento será el mismo y con el mismo tiempo de acción. Este

tiempo lo determina la red R-C cuyos valores dan la constante de tiempo. El

diodo se conecta para sacar rápidamente del estado intermedio al flip-flop una vez

producida la vuelta a 0. Durante

la carga del capacitor se encuentra en

oposición a la corriente, pero una vez que la salida Q vuelve a 0, queda en

directa para la carga obtenida, llevando este potencial a 0 casi

instantáneamente. En

ambos casos la entrada reset continúa funcionando, por lo tanto si se desea

anticipar la vuelta a 0 antes del tiempo establecido, simplemente se aplica

un pulso de nivel positivo en dicha entrada. El

comportamiento es igual al monoestable que hemos visto en la figura 5 de la

lección anterior, armado con un CD4069, solo que ahora no existe el

inconveniente de la división de tensiones que LOS DISPARADORES SCHMITT Este

tipo de circuitos integrados son similares a las clásicas compuertas y

separadores, a tal punto que en muchos casos podrían usarse unas en lugar de

las otras sin que se vea afectado el circuito lógico, sin embargo poseen

ciertas características que las distinguen y que deberemos tener en cuenta a

la hora de realizar un diseño. Por

lo pronto la conmutación hacia el estado alto y bajo ya no depende del estado

intermedio de la tensión de fuente (VDD), que en compuertas comunes sabemos

que se crea una situación de indecisión. Para

clarificar este concepto, supongamos una compuerta CD4011 alimentada con 12 V. Si

aplicamos una tensión de 7 V en sus entradas, interpretará un 1 con segundad.

Si ésta tensión fuese de 5 V interpretará un 0 también con seguridad. Pero si

la tensión es de 6 V se produce el estado de indecisión y no sabrá que

"rumbo tomar', produciendo en su salida señales confusas. Esta

situación no se presenta en los disparadores schmitt ya

que la conmutación en el estado alto se produce cuando la tensión de entrada

supera el valor intermedio y se acerca a VDD, y la conmutación hacia el

estado bajo se produce cuando la tensión desciende también del estado

intermedio y se acerca a VSS o masa. La

tensión positiva que define el estado alto se conoce como VT+ y la tensión

negativa que define el estado bajo como VT-. La diferencia de tensión entre

una y otra es la denominada tensión de histéresis (VH). En la figura 7 vemos

los datos en resumen del integrado CD4093 de NATIONAL. Se

trata de cuatro compuertas nand de dos

entradas con disparador schmtt. Podemos

apreciar que es compatible pin a pin con el integrado CD4011 que también contiene cuatro

compuertas nand. Los

símbolos que representan un disparador schmtt en

cualquier circuito expresan la tensión de histéresis VH configurada por las

dos rayitas que significan VT+ y VT-. La

ventaja principal de este integrado (4093) sobre su similar 4011, reside en

su alta inmunidad al ruido, otorgada por los parámetros de histéresis, ya que

cualquier señal espúrea que no supere los

umbrales de VT+ ó VT- no producirá ningún cambio en su salida.

FIG.

6 - CONFORMACIÓN DE ONDA Y ELIMINACIÓN DE SEÑALES DE RUIDO En

la figura 6 observamos una señal digital que llega a una de las entradas que

incluye un alto nivel de ruido que incluso llega a deformar su cuadratura,

sin embargo la salida entrega una forma de onda perfectamente rectangular con

flancos bien definidos.

FIG.

7 CARACTERÍSTICAS DEL CIRCUITO INTEGRADO CD4093 Esto

significa que no solo el ruido no ha causado problemas, sino que además la

señal aparece limpia de interferencias. Observe

que el cambio de estado en la salida, hacia el 0, se produce cuando la señal

llega al nivel de VT+ (recuerde que las NAND son inversoras), y vuelve a

cambiar hacia el 1 cuando desciende al nivel de VT-. Por supuesto que si la señal de

ruido es tan intensa que supera los umbrales de VT, en la salida se verá

reflejado el problema, lo que dice a las claras que los disparadores schmitt son muy efectivos pero no hacen milagros.... En

el gráfico de la figura 6 podemos ver que el cambio de estado en la salida se

produce cuando la señal llega al nivel de VT+ en su ascenso hacia VDD

(tensión de fuente), éste nivel está bastante por encima del nivel

intermedio. Luego vuelve a cambiar cuando llega al nivel de VT- que se

observa está por debajo del nivel intermedio. Las señales de ruido, a pesar

de que son de una notable amplitud, no producen cambios en la salida debido a

que no llegan a "tocar" el nivel de VT+. Si

fuera necesario aumentar la inmunidad al ruido, deberán utilizarse

separadores inversores del tipo 40106 en las etapas críticas, ya que éstos

tienen una tensión de histéresis (VH) mayor que el 4093 como veremos en esta

misma lección. LOS

UMBRALES DE HISTÉRESIS (VH) En

la hoja de datos de NATIONAL encontramos la información sobre los niveles de

tensión de VH referidos a tres fuentes de alimentación, 5 V, 10 V, y 15 V.

Estos valores se refieren a la separación en términos de tensión que existe

entre el umbral VT- y VT+, y son valores típicos tomados a una temperatura

ambiente de 25°. Sin embargo el fabricante solo garantiza una VH de 0,1 VDD.

FIG.

8 NIVELES DE VT+ VT- Y VH DEL INTEGRADO CD4093 Esta

última cifra significa 0,1 volt de histéresis por

cada volt de alimentación. Así por ejemplo,

tendríamos una VH de 1,5 volt como mínimo con una

fuente de 15 V (0,1 X 15). De lo expuesto se aprecia que pueden existir

diferencias en los niveles de VH entre las distintas partidas y fabricantes,

y de hecho, he comprobado que efectivamente es así, aunque nunca estas

diferencias fueron tan notables como para llegar al mínimo que garantizan,

generalmente están en un valor mayor. Veamos en la figura 8 la representación

gráfica de estos parámetros. En

el ejemplo para 15 V expuesto se observa en que niveles de tensión se

producirán las conmutaciones hacia el nivel bajo (VT-) y alto (VT+), como así

también la "separación" (VH) entre uno y otro VT. EL

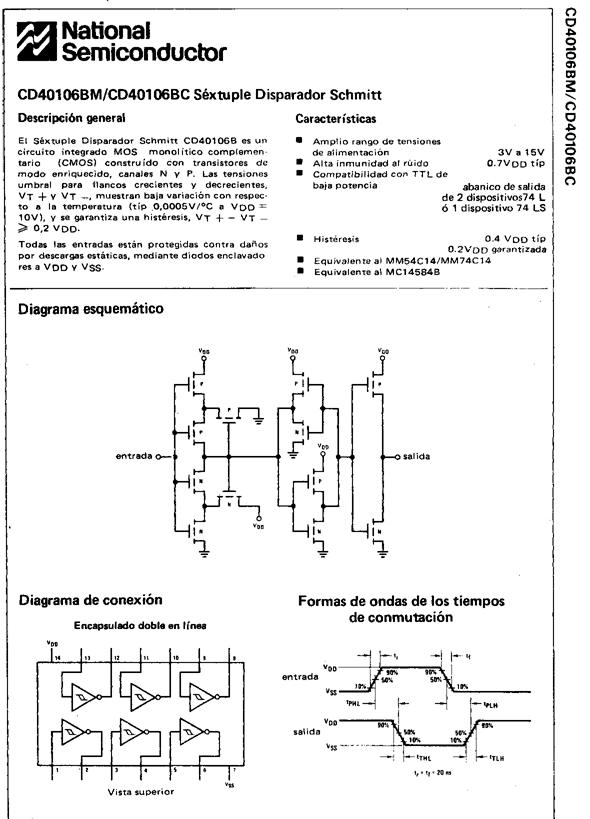

CIRCUITO INTEGRADO CD40106 Este

circulo integrado es básicamente igual al CD4069, o sea un séxtuple separador inversor, pero con lógica de

disparador schmitt. Incluso es compatible pin a pin por lo que podría

reemplazarlo sin Inconvenientes de manera directa, siempre que las

características del circuito lo permitan.

FIG.

9 - CARACTERÍSTICAS DEL INTEGRADO CD40106 En

la figura 9 observamos los datos sintetizados sobre éste integrado.

FIG.10

- NIVELES DE VT+ VT- Y VH DEL INTEGRADO CD40106 En

efecto, podemos ver que en este caso la VH es prácticamente el doble que en

el 4093, incluso se garantiza como mínimo 0,2 VDD mientras que en el anterior

era de 0,1 VDD. En la figura 10 hemos representado los parámetros de VH para

una tensión de alimentación de 15 V. Como

podemos ver los parámetros de VT+ y VT- nos dan una VH de 5 V y en el caso

anterior era de 2,7 V; este detalle hay que tenerlo en cuenta. De

acuerdo a estos números vemos que la VH corresponde a un tercio de la tensión

de alimentación, siempre considerando los valores típicos y a una temperatura

ambiente de 25°, por lo que será muy fácil determinar los parámetros con

otras tensiones, si bien pueden variar un poco, en la práctica se pueden despreciar.

Así por ejemplo, para una alimentación de 12 V, podemos considerar una VH de

4 V, y ubicaremos el VT- a los 4 V y el VT+ a los 8V, estas dos lecturas

referidas a masa. Este

es el momento de aclarar el concepto vertido en la lección anterior en el circuito

monoestable realizado con dos separadores. En esa oportunidad decíamos que

"R3 no debe superar el 30% aproximadamente del valor de R2....., y no

mas del 10% si se trata de disparadores schmitt". Pues

bien, ahora el alumno comprenderá porque. Supongamos que el monoestable en

cuestión realizado con separadores CD4069, está alimentado con una fuente de

15 V. El valor de R3 debe ser tal que asegure que a la entrada del inversor

en la patita 9 llegue una tensión superior a 7,5 V (valor intermedio) para que

se produzca la conmutación del mismo. Si en lugar del 4069 se instala un

40106, el valor de R3 debe asegurar que llegará una tensión superior a 10 V

(umbral de VT+) para producir el cambio. Por último si este monoestable

utiliza un 4093, la tensión que debe llegar tiene que ser superior a 8,85 V

(umbral de VT+). De este hecho surgen los porcentajes mencionados para R3. Digamos

también que la característica de histéresis hace que estos integrados sean

los ideales para conformar cualquier señal senoidal o

de forma irregular aplicada en su entrada, en una onda cuadrada perfectamente

definida en su salida, de modo similar a lo observado en la figura 7. OSCILADOR

ASTABLE No

hay nada mas fácil de realizar que un

oscilador astable a partir de un

disparador schmitt, sea éste una compuerta o

un simple inversor, ya que solo se necesita para producir la oscilación una

resistencia y un capacitor. En la figura 11

vemos como lograrlo con ambos componentes.

FIG.

11 OSCILADOR ASTABLE CON CONTROL En

ambos casos es posible la realización con un solo disparador gracias a la

histéresis propia, y su funcionamiento es el siguiente. La explicación vale

para los dos osciladores. Supongamos

que la salida se encuentra en nivel alto; el capacitor conectado

en la entrada, que está a 0, comienza a cargarse a través de la resistencia.

Cuando la tensión, que va creciendo, supera el nivel de umbral VT+, se

produce la conmutación y la salida pasa bruscamente a 0. Ahora el capacitor comienza a descargarse también a través de

la resistencia hacia la salida que dijimos está en 0. Cuando el potencial en

la entrada disminuye por debajo del umbral VT- se produce la conmutación

nuevamente y la salida pasa otra vez a 1 reiniciándose un nuevo ciclo. El

control del oscilador en la compuerta 4093, se efectúa en el terminal de la entrada libre. Un

estado alto en este terminal hará que el oscilador

funcione, y un 0 lo mantendrá en reposo. En

el inversor 40106 utilizamos un diodo para lograr el control, y su

disposición hará que la salida del mismo, en estado de reposo, adopte un

nivel alto ó bajo, según nuestra necesidad. Si se conecta para que funcione

con 1, el reposo será con 0; de este modo la entrada se mantendrá

permanentemente en 0 impidiendo la oscilación, y la salida en consecuencia

será 1. Si por el contrario queremos que funcione con 0, simplemente habrá

que dar vuelta el diodo, con lo cual en reposo la entrada permanecerá en 1

con lo cual tampoco oscilará, y naturalmente la salida será 0. Este

mismo sistema de control puede emplearse con la 4093 y obtener el potencial

que se requiera en su salida, para ello el terminal

libre se debe conectar directo a +B, y trabajar en el otro, instalando el

diodo del mismo modo que en el 40106. Aunque

no hemos hecho comentarios sobre la realización práctica de los circuitos

expuestos con los integrados 4093 y 40106, el alumno ya sabe de la

importancia de estos trabajos, ya que la comprobación del funcionamiento en

la plaqueta de ensayos fija mucho mas los

conocimientos que se adquieren. Por lo tanto, tome la plaqueta, los

componentes necesarios y manos a la obra. También

es importante que realice los osciladores propuestos con los integrados 4093

y 40106 y los enlace con el divisor por 2 de la figura 3, por

supuesto primero uno y después el otro, para ello debe armar los dos

integrados en la plaqueta y unir la salida del oscilador con la entrada reloj

del divisor por 2. En

la figura 12 damos un ejemplo de las posibilidades de interconexión de los

circuitos estudiados, enlazando la llave oscilante con el astable realizado con una compuerta 4093 y a su vez

ésta conectada con el flip flop divisor por 2. El

control se efectúa con el alambre de conexiones colocado en la entrada reloj

del 4013 (pin 3) Un

toque con la línea de +B pondrá en marcha todo el circuito y otro toque lo

llevará a reposo, dado que, como ya sabemos este flip flop cambia de estado en cada pulso positivo en la

entrada reloj. En

la puesta en marcha la salida Q que está en 0, cambia a 1 y habilita el astable, luego otro toque lo lleva a reposo y la salida

vuelve a 0, con lo cual se detiene el oscilador. Mediante

los diodos led observará la frecuencia de

salida del oscilador y la de salida del divisor por 2, esta última tendrá la

mitad de la frecuencia de la primera. Ya

sabe que la frecuencia en el astable la

determinan los valores de capacidad y resistencia, mayor valor en alguno de

ellos o en ambos, menor frecuencia y viceversa. Experimente

con otros valores a los indicados, incluso puede conectar un electrolítico en

lugar del capacitor de .1 y vea las

diferencias.

FIG.12

- UNO DE LOS ENLACES POSIBLES Digamos

por último que si lo desea puede combinar estos circuitos con otros ya

realizados en lecciones anteriores, por ejemplo, flips flops de distinto tipo, el duplicador de

frecuencia etc.Aunque conectamos

diodos led para ver los efectos, no deje

de usar la sonda para comprobar los cambios de estado que se producen en

distintas partes de los circuitos. Lista

de materiales que envía el Instituto que se suman a los ya recibidos: 1

- Circuito integrado CD4013 / 1 - Circuito integrado CD4093 / 1 - Circuito

integrado CD40106 RADIO INSTITUTO

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

E-mail: E-mail: radioinstituto@gmail.com - Sitio

web: http://www.radioinstituto.com/ |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||